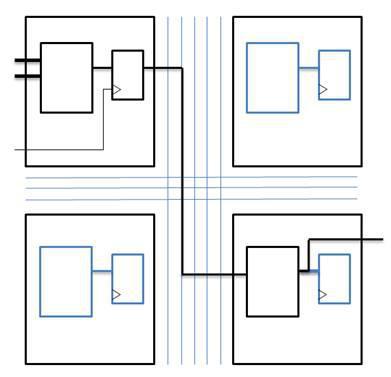

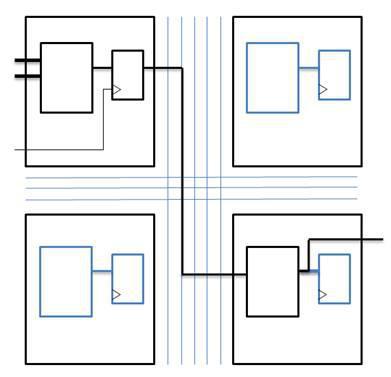

Программируемые микросхемы с архитектурой FPGA (FieldProgrammableGateArray – Программируемые Пользователем Вентильные Матрицы) имеют в основе набор конфигурируемых блоков (логических ячеек), содержащих базовые компоненты цифровой логики – логические элементы и триггеры. Отдельные ячейки соединяются друг с другом с помощью программируемых трассировочных линий, как показано на рис. 3.1.

Рис. 3.1 Фрагмент ПЛИС с архитектурой FPGA (Field-ProgrammableGateArray – программируемые пользователем вентильные матрицы)

На рис. 1.1. видно, что две ячейки из всего массива оказались запрограммированы на реализацию определенной логической функции. Поскольку для реализации схемы одной ячейки оказалось недостаточно, ее выход был подключен к входу другой ячейки, для чего задействованы трассировочные линии FPGA. Чтобы реализовать такую схему, необходимо задать режимы работы отдельных компонентов внутри ячеек, а также активировать цифровые ключи, соединяющие отдельные сегменты трассировочных линий. Настройки компонентов и информация о включенных/выключенных коммутаторах хранится в специальной памяти внутри FPGA. Эта память выполнена по технологии SRAM, поэтому имеет неограниченное число циклов перезаписи, однако теряет информацию при пропадании питания. Поэтому при включении микросхему FPGA необходимо запрограммировать – подать на специальный интерфейс файл конфигурации.

На практике программирование ячеек и формирование трассировочных линий выполняется автоматически, с помощью системы автоматизированного проектирования. Структура файла конфигурации является строго конфиденциальной информацией, и формирование такого файла может быть выполнены только с помощью САПР Xilinx.

Можно видеть основные особенности подхода, реализованного в FPGA. Во-первых, эти ПЛИС подразумевают гранулярность схемы. Это означает, что сложные схемы с неравномерным использованием компонентов все равно необходимо будет приводить к базовым возможностям логических ячеек, причем весьма вероятно, что какие-то возможности ячеек окажутся незадействованными.

Во-вторых, программируемые трассировочные линии имеют большую задержку распространения сигнала по сравнению с металлическими соединениями интегральных микросхем. Поэтому рабочие частоты ПЛИС оказываются меньше, чем частоты микросхем, выполняемых обычным способом.

Таким образом, проекты на базе ПЛИС оказываются дороже и медленнее решений на базе стандартных (StandardProduct) или специализированных микросхем (ASIC, ASSP). Тем не менее, на протяжении развития цифровой микроэлектроники производство ПЛИС демонстрировало устойчивый рост. Это связано с тем, что стоимость подготовки производства интегральных схем постоянно растет, и, например, для технологического процесса с нормой 32 нм достигает 200 млн. USD (по данным 2012 г.). Поэтому разработка специализированной микросхемы оказывается экономически целесообразной только для массового производства. Поэтому ПЛИС являются подходящей элементной базой для разработки цифровых устройств с уникальной архитектурой, выпускаемых небольшими тиражами.

Другими преимуществами ПЛИС являются возможность реализации параллельных вычислительных структур и достижение высокой степени интеграции компонентов системы. Эти свойства проистекают из возможности реализовать в ПЛИС множество небольших блоков, реализующих простые операции. ПЛИС с архитектурой FPGA традиционно используются в задачах цифровой обработки сигналов, поскольку обеспечивают очень высокие показатели производительности (до 5,8 TMAC/сек). Другим крупным сегментом применения FPGA являются коммуникационные устройства, прежде всего магистральное оборудование проводной связи.

Компания Xilinx с 1985 года выпускает ПЛИС, представляющих основные архитектуры, имеющиеся в микроэлектронике – CPLD и FPGA. На протяжении развития микроэлектронной технологии микросхемы с архитектурой FPGA развивались все более активно, так как возможности их масштабирования позволяют создавать кристаллы с сотнями тысяч и миллионами логических ячеек. В настоящее время именно FPGA являются наиболее универсальными и мощными программируемыми микросхемами, позволяющими реализовать широкий спектр цифровых устройств. Микросхемы CPLD в основном используются в качестве замены дискретных цифровых компонентов.

Xilinx, как и большинство производителей ПЛИС, является fabless-компанией, т.е. не имеет собственного производства, а заказывает изготовление микросхем по разработанным проектам сторонним компаниям. Соответственно, по мере освоения новых технологических процессов мировыми производителями, Xilinx имеет возможность выпустить новое поколение ПЛИС с использованием освоенного технологического процесса. Это и наблюдалось на протяжении существования компании.

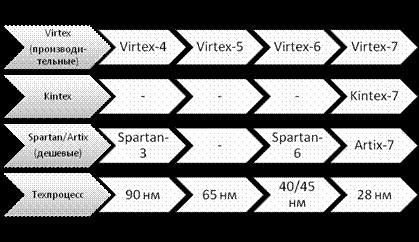

В конце 90-х годов основной линейкой FPGA среди продукции Xilinx была серия XC4000 (семейства XC4000E, XC4000XL и XC4000XLA). Архитектура XC4000 оказалась довольно удачной, но оказалось, что в целом ряде проектов возможности стандартной логической ячейки ПЛИС используются далеко не полностью. Возникла естественная альтернатива – использовать дорогие устройства с максимальной производительностью и полным набором функциональных возможностей, или напротив, дешевые ПЛИС, обеспечивающие базовые функции, требующиеся для большинства типовых проектов. В результате в номенклатуре изделий Xilinx появились различные серии FPGA, отвечающие упомянутым альтернативам. Стандартное недорогое решение представляла серия Spartan, на смену которой пришли серии Artix (минимальная стоимость) и Kintex (умеренная стоимость при высокой производительности в задачах цифровой обработки сигналов), тогда как наилучшие технические характеристики достигаются в серии Virtex. На данный момент наиболее современными являются семейства серии 7 – Artix-7, Kintex-7, Virtex-7.

Рис.3.2 Диаграмма соответствия поколений FPGAXilinx технологическим процессам

Отдельным направлением ПЛИС, анонс которого состоялся в 2011 году, являются микросхемы класса AllProgrammableSoC («полностью программируемые системы на кристалле»). Первыми из микросхем такого типа являются APSoC семейства Zynq-7000. Они включают в себя процессорное ядро ARM и матрицу программируемых логических ячеек, аналогичных применяемым в Artix или Kintex.

Кроме того, Xilinx выпускает микросхемы с архитектурой CPLD (ComplexProgrammableLogicDevices) семейств XC9500XL, CoolRunner, CoolRunner-II и средства загрузки конфигурации – микросхемы флеш-памяти и контроллер CF-карт.