Программируемые логические интегральные схемы с архитектурой FPGA (FieldProgrammableGateArray) организованы в виде массива логических ячеек, состоящих из блоков комбинаторной логики (Look-UpTable, LUT) и триггеров. В исходном состоянии FPGA не реализует какой-то конкретной схемы, а функциональность приобретает после операции программирования – занесения в специальную конфигурационную память значений, управляющих цифровыми ключами, соединяющими отдельные элементы на кристалле FPGA. Также конфигурационная память управляет логическими генераторами, мультиплексорами и другими цифровыми узлами, которые в разных схемах могут выполнять различные функции.

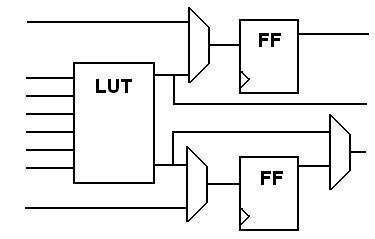

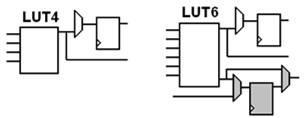

Рис. 3.3 Упрощенная схема логической ячейки FPGAVirtex-6 и Spartan-6,

Virtex-7, Kintex-7, Artix-7

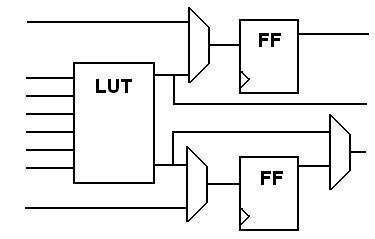

Комбинаторная логика реализуется в таких ячейках путем заполнения таблиц истинности, представляющих собой модули памяти. Комбинация состояний на входах для такого модуля является адресом ячейки, хранящей требуемое значение выхода. Такой подход позволяет реализовать произвольную логическую функцию, поскольку независимо от сложности схемы все возможные состояния выхода записываются в память. Эта память представляет собой ОЗУ, и ее содержимое записывается в процессе загрузки конфигурации FPGA.

Рис. 3.4 Принципы реализации комбинаторной логики в ПЛИС FPGA

Логические ячейки организованы в ПЛИС в виде прямоугольной матрицы. Входы и выходы ячеек подключаются к программируемым трассировочным линиям, проложенным в вертикальном и горизонтальном направлениях. Отдельные фрагменты линий коммутируются с помощью цифровых ключей. Это позволяет соединить любые ячейки FPGA, замыкая соответствующие ключи. Состояния ключей (замкнуты или разомкнуты) записываются в соответствующие разделы конфигурационной памяти. В процессе проектирования разработчику не требуется задавать состояния ключей и таблиц истинности непосредственно, поскольку это выполняет САПР ПЛИС на основе анализа введенной схемы. Более того, формат конфигурационного потока, загружаемого в FPGA, является закрытым, а его формирование производится исключительно программными средствами компании-производителя.

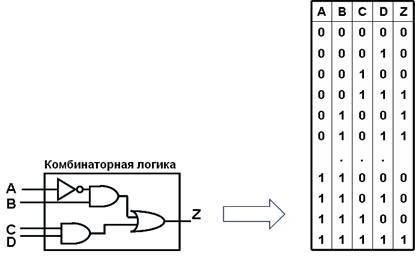

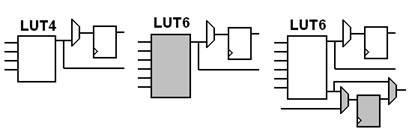

На протяжении развития FPGA архитектура логической ячейки претерпевала изменения, которые схематично можно проиллюстрировать рис.

Рис. 3.5 Изменения в архитектуре логической ячейки в различных поколениях FPGAXilinx (Virtex-4, Virtex-5, Virtex-6, серия 7)

Рис. 3.6 Изменения в архитектуре логической ячейки в различных поколениях

FPGAXilinx (Spartan-3, Spartan-6)

Начиная с 6-й серии, логическая ячейка получила унифицированную архитектуру в различных сериях. Эта же архитектура сохранена для ПЛИС 7-й серии – Virtex-7, Kintex-7, Artix-7.

Кроме собственно логических ячеек и блоков ввода-вывода, современные FPGA содержат большое количество аппаратных блоков, реализующих часто используемые в цифровой схемотехнике функции. Смысл размещения на кристалле таких блоков состоит в том, что те же узлы, выполняемые с помощью логических ячеек, будут иметь существенно больший размер и пониженное быстродействие. В то же время аппаратная реализация часто используемых блоков несущественно увеличивает площадь кристалла и стоимость, зато весьма благоприятно влияет на характеристики проекта в целом.

К аппаратным блокам, размещаемым в FPGA, относятся:

– блоки синхронной статической двупортовой памяти BRAM;

– блоки цифровой обработки сигналов «умножение с накоплением» XtremeDSP;

– формирователитактовыхсигналов MMCM (Multi-Mode Clock Managers) и PLL (Phase-Locked Loop);

– скоростные последовательные приемопередатчики (MGT, Multi-GigabitTransceivers);

– контроллеры Ethernet MAC (Virtex-4, 5, 6);

– контроллеры PCI Express endpoint;

– процессорныеядра PowerPC (Virtex-II Pro, Virtex-4 FX, Virtex-5 FXT), ARM (Zynq-7000).

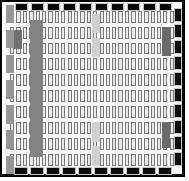

Рис. 3.7FPGA семейства Spartan-6

На рис.3.7 показано изображение FPGA семейства Spartan-6. Видно, что кроме логических ячеек, современные FPGA содержат большое количество специализированных модулей, облегчающих реализацию широко распространенных задач цифровой схемотехники.

Микросхемы серии Virtex, начиная с семейства Virtex-4, выполнены по архитектуре ASMBL (AdvancedSiliconModularBlocks), предложенной Xilinx. В рамках этого подхода FPGA набираются из колонок ресурсов различного типа – логических ячеек, блоков цифровой обработки сигналов, модулей памяти, высокоскоростных последовательных приемопередатчиков. Комбинируя различное число колонок, оказывается возможным быстро разрабатывать микросхемы, нацеленные на решение задач разного типа. В терминологии Xilinx такие разновидности FPGA, отличающиеся соотношением основных ресурсов, называются платформами. Схематическое изображение FPGAVirtex-6, выполненной по третьему поколению ASMBL, показана на рис. 3.8.

Рис. 3.8 FPGA семейства Virtex

На рис. 3.8 видно, что кроме программируемых логических ячеек, на кристалле находятся и аппаратные модули, перечисленные выше.

Понятие «платформа» было распространено и на семейство Spartan-6 из организационных соображений. Несмотря на то, что формально это семейство не выполнено по архитектуре ASMBL, с точки зрения конструкторов систем на базе ПЛИС удобно выбирать элементную базу из набора микросхем, различающихся не только количеством основных функциональных блоков, но и их соотношением.

Семейство Virtex-7 в настоящее время состоит из трех подсемейств (платформ):

– Virtex-7

– Virtex-7XT

– Virtex-7HT

В семействе Kintex-7 не используется разделение на платформы. Это семейство оптимизировано для цифровой обработки сигналов, и имеет лучшее соотношение производительность/цена, чем Vitrtex-7 при той же тактовой частоте.

Семейство Artix-7 сменило серию Spartan в качестве FPGA малой стоимости.

В таблице 3.1 приведены общие характеристики FPGA серии 7.

Таблица 3.1 Общие характеристики FPGA серии 7

|

Максимальное значение параметра |

Artix-7 |

Kintex-7 |

Virtex-7 |

|

Логических ячеек, тыс |

215 |

480 |

1955 |

|

Блочной памяти, Мб |

13 |

34 |

65 |

|

Секций DSP |

740 |

1920 |

3600 |

|

Пиковая производительность цифровой обработки сигналов для фильтров с симметричными коэффициентами, GMAC/c |

930 |

2845 |

5335 |

|

Приемопередатчиков |

16 |

32 |

96 |

|

Максимальная скорость передачи, Гб/с |

6,6 |

12, 5 |

28,05 |

|

Пиковая пропускная способность приемопередатчиков, Гб/с |

211 |

800 |

2784 |

|

Интерфейсы PCI Express |

Gen2x4 |

Gen2x8 |

Gen3x8 |

|

Скорость обмена по интерфейсам памяти, Мб/c |

1066 |

2133 |

2133 |

|

Внешних выводов |

500 |

500 |

1200 |

Семейство Zynq 7000 состоит из 4 микросхем, выполненных по техпроцессу с нормами 28 нм. Все ПЛИС имеют одну и ту же процессорную подсистему на основе двухядерного процессора ARM. Характеристики ядра ARM в составе Zynq-7000 представлены ниже:

- Ядро: сдвоенное Cortex-A9, тактовая частота 667/773/800/1000 МГц (в зависимости от градации скорости).

- Расширения ядра: NEON™, плавающая точка одинарной и двойной точности.

- Кэш первого уровня: 32 кб инструкций, 32 кб данных на каждое ядро.

- Кэш второго уровня: 512 кб.

- Поддержка внешней памяти: DDR2, DDR3, LPDDR2.

- Каналов ПДП: 8.

- Периферия:

- USB 2.0 (OTG) c ПДП – 2;

- Трехрежимный (10/100/1000) Etnernetc ПДП – 2;

- SD/SDIO с ПДП – 2;

- UART – 2;

- CAN 2.0B – 2;

- I2C – 2;

- SPI – 2;

- GPIO – 32 бита.

- Шифрование – AES и SHA 256 бит.

- Мультиплексируемых линий памяти и ввода-вывода – 54.

- Интерфейсы к программируемым ресурсам:

- AXI 32 бита Master – 2;

- AXI 32 бита Slave – 2;

- AXI 64/32 бита, интерфейс с памятью – 4;

- AXI 64 бита ACP;

- Прерываний – 16.

Характеристики программируемой логики ПЛИС Zynq 7000 приведены в табл. 1.2.

Таблица 3.2 Состав семейства Zynq-7000

|

ПЛИС |

Z-7010 |

Z-7020 |

Z-7030 |

Z-7045 |

|

Программируемых логических ячеек (вентилей ASIC) |

28 K (430 K) |

85 K (1,3 M) |

125 K (1,9 M) |

350 K (3,5 M) |

|

Блоков памяти (по 36 кб) |

60 |

140 |

265 |

545 |

|

Секций DSP (18x25 MACC) |

80 |

220 |

400 |

900 |

|

Пиковая производительность DSP для КИХ с симметричными к-тами, GMAC/s |

100 |

276 |

593 |

1334 |

|

Блоков PCI Express |

– |

– |

Gen2 x4 |

Gen2 x8 |

|

АЦП |

2x12 бит, 1 М выборок/с, 17 дифф. каналов |

|||

|

Шифрование |

AES и SHA 256-бит |

|||

|

Блоков ввода-вывода, 3,3В |

100 |

195 |

100 |

200 |

|

Блоков ввода-вывода, 1,8 В |

– |

– |

150 |

150 |

|

Высокоскоростных приемопередатчиков |

– |

– |

4 |

12 |

Микросхемы Zynq-7010 и Zynq-7020 выполнены на базе программируемых ресурсов семейства Artix, а Zynq-7030 и Zynq-7045 – на базе Kintex. Это отражается на пиковой производительности подсистемы цифровой обработки сигналов – в младших ПЛИС тактовая частота блока ниже. Также в младших ПЛИС нет блоков PCIExpress и высокоскоростных приемопередатчиков.

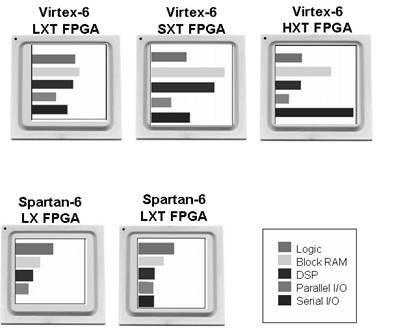

Платформы семейств Virtex-6 и Spartan-6 показаны на рис. 3.9.

Рис. 3.9 Платформы семейств Virtex-6 и Spartan-6

Платформы имеют следующее целевое назначение:

– Virtex-6 LX/LXT/CXT – платформы с большим объемом логики;

– Virtex-6 SXT – платформа, предназначенная для цифровой обработки сигналов;

– Virtex-6 HXT – платформа, предназначенная для построения скоростных телекоммуникационных устройств на основе приемопередатчиков GTH с пропускной способностью до 11,2 Гбит/с;

– Spartan-6 LX – недорогое семейство, предназначенное для реализации устройств преимущественно с помощью логических ячеек;

– Spartan-6 LXT – семейство с высокоскоростными последовательными приемопередатчиками GTP (до 3,25 Гбит/с).

В таблице 3.3 приведены общие характеристики FPGA серии 6.

Таблица 3.3 Общие характеристики FPGA серии 6

|

Максимальное значение параметра |

Spartan-6 |

Virtex-6 |

|

Логических ячеек, тыс |

150 |

760 |

|

Блочной памяти, Мб |

4,8 |

38 |

|

Секций DSP |

180 |

2016 |

|

Пиковая производительность цифровой обработки сигналов для фильтров с симметричными коэффициентами, GMAC/c |

140 |

2419 |

|

Приемопередатчиков |

8 |

72 |

|

Максимальная скорость передачи, Гб/с |

3,2 |

11,18 |

|

Пиковая пропускная способность приемопередатчиков, Гб/с |

50 |

536 |

|

Интерфейсы PCI Express |

Gen1x1 |

Gen2x8 |

|

Скорость обмена по интерфейсам памяти, Мб/c |

800 |

1066 |

|

Внешних выводов |

576 |

1200 |

FPGAXilinx обозначаются следующим образом:

XC6VLX240T-1FFG1156C

XC – комбинация символов, общая для всех ПЛИС Xilinx;

6V – обозначение семейства Virtex-6;

LX240T – микросхема внутри семейства;

-1 – класс скорости (speedgrade);

FFG1156 – корпус (символ G соответствует бессвинцовому исполнению);

C – температурный диапазон (C – коммерческий, I – промышленный).

Понятие «класс скорости» (speedgrade) является обобщенным показателем, характеризующим быстродействие данного экземпляра ПЛИС. В отличие от ранних семейств, для которых достаточно было указать наиболее характерный параметр, относящиеся к быстродействию (например, время распространения сигнала через кристалл или по одной логической ячейке), быстродействие сложных FPGA последних поколений уже не может быть адекватно описано единственным числом. Вместо этого используется селекция экземпляров микросхем в партии, проверка их способности обеспечивать требуемые характеристики быстродействия, и присвоение класса скорости. Для этого параметра Xilinx использует принцип «чем больше, тем лучше». Как правило, FPGAXilinx имеют 2 или 3 класса скорости, отличающиеся по быстродействию на 15-20%.

Одной из тенденций в цифровой микроэлектронике является снижение уровня напряжения питания интерфейсов. В настоящий момент актуальные FPGA поддерживают следующие максимальные напряжения питания (табл. 3.4):

Таблица 3.4 Напряжения питания цифровых интерфейсов

|

Семейство |

Максимальное напряжение, В |

|

Spartan-6 |

3,3 |

|

Virtex-6 |

2,5 |

|

Artix-7 |

3,3 |

|

Kintex-7 |

3,3, некоторые 1,8 |

|

Virtex-7 |

1,8, некоторые 3,3 |

В таблице можно видеть, что ПЛИС семейств Kintex-7 и Virtex-7 имеют два напряжения для питания интерфейсов. Поскольку интерфейсы с меньшим напряжением питания поддерживают большую скорость передачи сигналов, они актуальны для ПЛИС, нацеленных на достижение максимальной производительности. С другой стороны, напряжение 3,3 В более универсально, поскольку допускает подключение к ПЛИС более широкой номенклатуры компонентов. Поэтому в семействах Kintex и Virtex реализованы два типа интерфейсных блоков:

– HR (HighRange) – поддерживают напряжение питания до 3,3 В;

– HP (HighPerformance) – поддерживают напряжение питания до 1,8 В, обеспечивают большую скорость передачи сигналов.

Основные характеристики FPGA приведены в табл. для семейств Virtex-6 LX, LXT, SXT, табл. для Spartan-6 LX и табл. для Spartan-6 LXT.

ПЛИС платформы HXT содержат по 24 приемопередатчика GTH, начиная с второго по объему устройства HXT255. Остальные приемопередатчики (24 или 48 на кристалл) представляют собой модули GTX, скорость передачи которых ограничена величиной 6,5 Гбит/с.

Такое количество приемопередатчиков, которые обеспечивают суммарную пропускную способность более 200 Гбит/с только для модулей GTH, дают основания для выбора соответствующих сфер применения подобных устройств. Можно обратить внимание, что приемопередатчики с пониженной скоростью присутствуют в ПЛИС HXT в удвоенном количестве, что позволяет, например, разрабатывать устройства для взаимного преобразования пакетов между сетями 10 Гбит/с и сетями с меньшей скоростью.

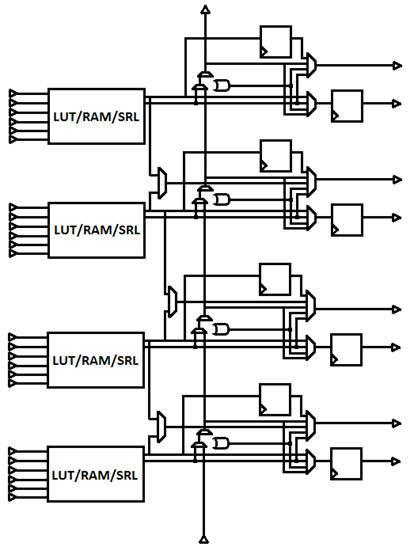

Логические ячейки

Общая структура

Логические ячейки (logiccell) являются основным программируемым элементом, определяющим возможности ПЛИС FPGA. Основными компонентами ячейки являются логический генератор и триггер. Ячейки (т.е. LUT и соответствующие им триггеры и мультиплексоры) объединяются в секции (slice). Секции, в свою очередь, объединяются в конфигурируемые логические блоки (КЛБ, ConfigurableLogicBlock, CLB).

Схема секции FPGA серии 7 показана на рис. 3.9.

Рис. 3.9 Схема секции FPGA серии 7

Логический генератор

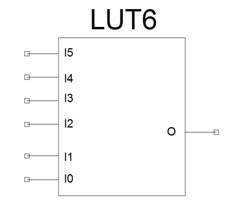

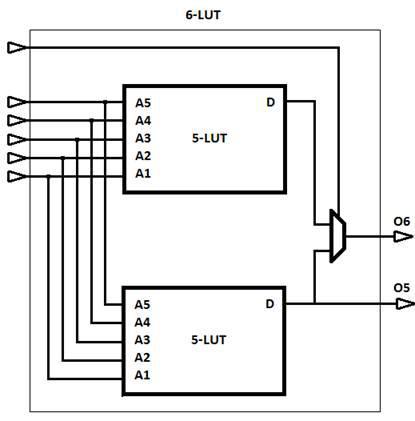

Логический генератор (LUT, Look-UpTable) представляет собой статическую память, инициализируемую в процессе загрузки конфигурации FPGA. Графическое изображение логического генератора представлено на рис.

Рис. 3.10 Графическое изображение логического генератора

Логический генератор (LUT) реализует любую функцию с не более чем 6 операндами. Кроме того, возможно использование LUT в режиме с частично совмещенными входами, когда память разбивается на два фрагмента по 32 бита, давая возможность сформировать две логические функции с не более чем 5 операндами каждая. При этом, поскольку в самой LUT всего 6 входов, часть входов должна быть обобщена (см. рис. 3.11). Такой режим автоматически используется САПР по мере возможности.

Рис. 3.11 Использование LUT в режиме совместного использования входов

Синтезаторы автоматически используют LUT для реализации комбинаторных схем.

Распределенная память

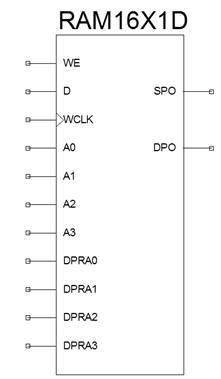

Логические генераторы могут также использоваться в режимах распределенной памяти (distributedmemory) и сдвиговых регистров. Поскольку логический генератор представляет собой элемент статической памяти, который хранит таблицу истинности в явном виде, его можно использовать по прямому назначению – в качестве обычного компонента памяти.

Рис. 3.12 Графическое изображение элемента двупортовой распределенной памяти

Распределенная память может работать в однопортовом или простомдвупортовом (simpledual-port) режимах. Простой двупортовый режим имеет то ограничение, что только один порт может использоваться для чтения и записи, а второй предназначен только для чтения. Показанный на рис. элемент распределенной памяти имеет следующие сигналы:

– we – сигнал разрешения записи;

– d – данные для записи;

– wclk – вход тактового сигнала;

– a – адрес для записи;

– dpra – адрес для чтения, второй порт (dualportreadaddress);

– spo – выход первого порта (singleportoutput);

– dpo – выход второго порта (dualportoutput).

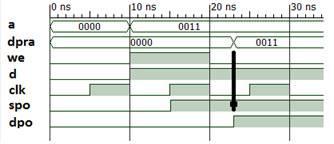

Временные диаграммы работы распределенной памяти показаны на рис. 3.13.

Рис. 3.13 Временные диаграммы работы распределенной памяти

На рис. видно, что запись в память происходит синхронно (на рис. – в момент времени 15 нс, когда данные d = 1 записываются по адресу addr = 00112 = 310), а чтение – асинхронно. В момент времени 23 нс (т.е. даже при отсутствии фронта тактового сигнала) изменение адреса на входе dpra приводит к соответствующему изменению выхода dpo. Аналогично, изменение состояния входа a немедленно приводит к появлению на выходе spo значения из ячейки с адресом a.

Распределенная память удобна для организации небольших блоков данных – буферов, линий задержки, небольших таблиц. Реализация больших блоков на распределенной памяти в общем случае нецелесообразна из-за сильной фрагментации такого блока. Для объемов в 512 слов и более удобнее использовать блочную память.

Тем не менее, распределенная память обладает важным свойством, отсутствующим у блочной памяти – она допускает асинхронное чтение.

Сдвиговый регистр

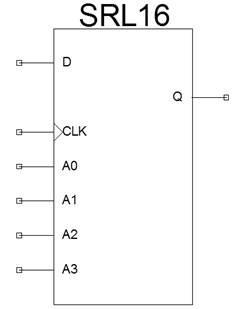

Другой вариант использования логического генератора – реализация на его базе сдвигового регистра. Графическое изображение такого компонента показано на рис. 3.14.

Рис. 3.14 Графическое изображение сдвигового регистра, реализованного на базе логического генератора

Сдвиговый регистр имеет следующие сигналы:

– d – данные для записи в сдвиговый регистр;

– clk – тактовый сигнал;

– a – адресный вход;

– q – выход данных.

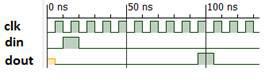

В простейшем варианте сдвиговый регистр может представлять собой модуль, задерживающий входной сигнал din на N тактов. Временные диаграммы работы 8-разрядного сдвигового регистра показаны на рис. 3.15.

Рис. 3.15 Временные диаграммы работы сдвигового регистра

LUT в режиме сдвигового регистра может использоваться совместно с триггером той же логической ячейки, увеличивая глубину сдвигового регистра на 1.

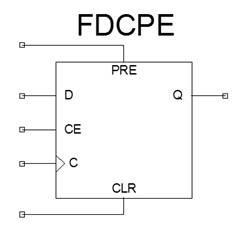

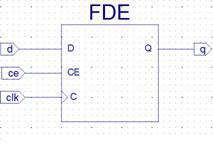

Триггеры

Логические ячейки FPGA содержат два триггера. Таким образом, каждая секция имеет 8 триггеров. Графическое изображение триггера (в одном из возможных вариантов) показано на рис. 3.16.

Рис. 3.16 Графическое изображение триггера

Триггер имеет следующие сигналы:

– С – вход тактового сигнала;

– D – вход данных;

– CE – вход разрешения записи (clockenable);

– CLR – вход асинхронного сброса (clear);

– PRE – вход асинхронной установки в логическую единицу (preset);

– R – вход синхронного сброса (reset);

– S – вход синхронной установки в логическую единицу (set);

– Q – выход данных.

Примечание: физически существует только один сигнал сброса/установки SR. Сброс, установка (синхронные или асинхронные) реализуются путем комбинирования триггера с другими ресурсами ячейки.

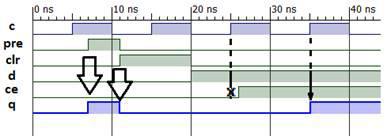

Триггер работает следующим образом. Появление логической единицы на асинхронном входе немедленно сбрасывает или устанавливает выход триггера. В остальных случаях все изменения триггера происходят по фронту тактового сигнала (вход C, от clock, тактовый вход также часто обозначается как clk). Временные диаграммы работы триггера показаны на рис. 3.17.

Рис. 3.17 Временные диаграммы работы триггера

Анализируя диаграмму на рис. 3.17, можно заметить, что появление сигналов pre и clr немедленно изменяет состояние триггера. Если эти сигналы неактивны, запись в триггер производится по фронту тактового сигнала. В момент времени 25 нс логическая единица с входа d не была записана на выход, поскольку сигнал ce в этот момент был неактивен. Однако запись состоялась в момент времени 35 нс, при активном сигнале ce. Для всех управляющих сигналов активным уровнем считается логическая единица.

Для логической секции последних поколений FPGAXilinx существует понятие controlset. Оно соответствует набору управляющих сигналов (clk, ce, sr), которые должны быть идентичны для всех триггеров секции. Это означает, например, что невозможно использовать сигнал ce только для одного триггера в секции. Следует обратить внимание, что тактовый сигнал также включен в controlset, т.е. все триггеры должны тактироваться одним и тем же тактовым сигналом. На практике такое ограничение означает, что при необходимости использовать разные управляющие сигналы соответствующие триггеры будут помещены в разные секции.

4Ограничения, связанные с controlset, не являются значимыми на начальном этапе знакомства с разработкой проектов на базеПЛИС. Размещение триггеров производится САПР с учетом этих ограничений. Негативный эффект может проявиться при задании разработчиком проектных ограничений по размещению отдельных компонентов проекта – при разных наборах управляющих сигналов триггеры не смогут быть помещены в одну секцию, если разработчик все же пытается сделать это с помощью проектных ограничений.

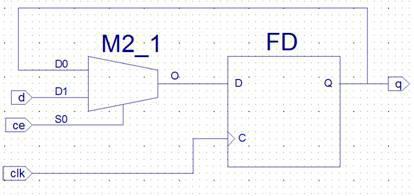

Существует методы преобразования логических схем, позволяющие избавиться от необходимости использования управляющих входов разрешения записи, сброса и установки. Например, если требуется исключить использование входа ce, влияние этого входа можно имитировать записью старого значения в триггер. На рис. 3.18 показаны исходная схема триггера с входом ce и эквивалентная схема, использующая дополнительную логику для обеспечения аналогичного поведения. В схеме вход ce подается на мультиплексор, который в зависимости от своего сигнала управления S0 имеет на выходе значение с входа D0 (при S0 = 0) или D1 (при S0 = 1). При нулевом уровне сигнала ce (а значит, и S0) на выходе мультиплексора будет присутствовать старое значение триггера. Поэтому перезапись триггера, строго говоря, состоится, однако записано будет его предыдущее состояние. Если же ce = 1, мультиплексор подаст на вход данных сигнал d.

Рис. 3.18 Схема замещения триггера с входом ce эквивалентной схемой на базе D-триггера

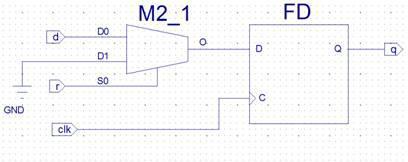

Аналогично можно получить замену триггера с входом синхронного сброса или установки. В этом случае мультиплексор подает на вход триггера фиксированный сигнал – логический ноль (или единицу), если на входе схемы действует активный сигнал сброса. Если же этого сигнала нет, на вход триггера подаются данные с входа d (см. рис. ).

Рис. 3.19 Схема замещения триггера с входом синхронного сброса эквивалентной схемой на базе D-триггера

4Следует по возможности использовать аппаратные входы триггеров, поскольку это экономит логические ресурсы и обычно приводит к большей производительности схемы и меньшему энергопотреблению.

Важным вопросом, на который стоит обратить внимание, является организация сброса триггеров. Отличием FPGA от дискретной логики является то, что триггеры FPGAимеют гарантированное начальное значение после включения питания. Значения всех триггеров (и других компонентов системы) записаны в конфигурационном файле, и инициализация выполняется с помощью специальных трассировочных ресурсов. Поэтому отдельные цепи сброса, предусматриваемые разработчиком в схеме для обеспечения начального состояния триггера, являются избыточными. По умолчанию все триггеры инициализируются нулем, если иное не задано разработчиком. Самый простой способ – объявление сигнала с начальным значением:

signalreg1 : std_logic := ‘1’;

В этом примере на VHDL объявляется триггер с именем reg1, которому присваивается начальное значение 1. Это значение будет корректно учитываться средствами моделирования, и будет записано в конфигурационный файл FPGA.

Триггеры автоматически синтезируются из поведенческого описания схемы. Использование специальных сигналов, таких как ce, r/s, clr/pre, зависит от настроек синтезатора и по умолчанию включено.