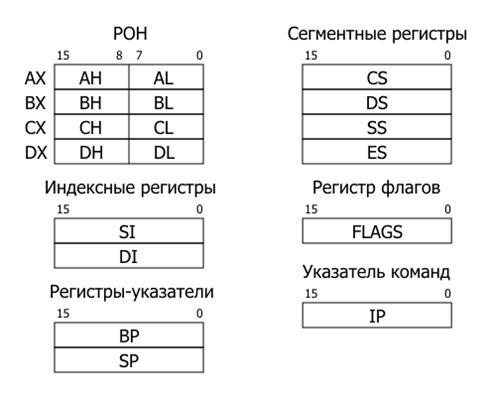

Под регистровой моделью понимается описание набора регистров процессора, их разрядности, способа организации, методов доступа, основных особенностей и пр. Пример регистровой модели процессора 8086 приведен на рис. 5.4.

Рис. 5.4 Регистровая модель процессора 8086

На рис. 5.4 показаны регистры, доступные программисту при использовании машинных кодов (или языка ассемблера). Наиболее универсальными являются регистры общего назначения (РОН), которые в 8086 обозначаются с использованием символов латинского алфавита A, B, C, D. Регистры имеют 16 разрядов, их младшая часть дополнительно обозначается символом L (Low), а старшая – H (High). Весь регистр обозначается дополнительным символом X. Таким образом, AX соответствует всем 16 разрядам первого регистра общего назначения, а доступ к двум его 8-разрядным половинам производится по именам AH, AL.

Для операций с объектами в памяти используются индексные регистры. Их имена являются сокращениями от SourceIndex (SI) и DestinationIndex (DI), т.е. «индекс источника» и «индекс приемника» соответственно.

Также в 8086 присутствуют указатели на области памяти стека и стекового кадра SPи BP, сводный регистр флагов (особых признаков результата последней операции) и сегментные регистры.

Для сравнения на рис. 5.5 показана регистровая модель процессора 80386.

Рис. 5.5 Регистровая модель процессора 80386

Сравнение рисунков наглядно показывает, что в последующем процессоре семейства 80x86 был сохранен общий подход к формированию «картины» регистров, однако произошли существенные изменения. Разрядность регистров была увеличена с 16 до 32, а также добавлено большое количество специальных и управляющих регистров.

Для сравнения на рис. 5.6 показана регистровая модель другой популярной процессорной архитектуры ARM. Аббревиатура ARM обозначает (AdvancedRISCMachine), данная архитектура появилась в середине 80-х годов 20 века. На рис. 5.6. видно, что процессор ARM может находиться в двух состояниях, в каждом из которых ему доступны различные сочетания регистров.

Рис. 5.6 Регистровая модель процессоров ARM

Над регистрами процессора, теоретически, могут быть выполнены любые операции, предусмотренные цифровой схемотехникой. Однако в практических реализациях набор этих операций ограничен. Более того, различные регистры процессора могут участвовать в строго определенных операциях, различаясь, таким образом, по назначению. Можно вкратце перечислить основные типы регистров, исходя из набора операций, доступных для них.

1) Регистр общего назначения.

В данную категорию попадает основная масса регистров, так или иначе доступных программисту и активно используемых при выполнении основной массы команд. Как правило, с этими регистрами возможно выполнение наибольшего числа команд.

2) Аккумулятор

Аккумулятор является преимущественным получателем данных. В различных процессорах команды, использующие аккумулятор, могут иметь более короткую форму записи, выполняться быстрее, или же аккумулятор является единственно возможным получателем результата. Также аккумулятор может иметь увеличенную разрядность по сравнению с другими регистрами (что актуально для сигнальных процессоров, которые при выполнении умножения с накоплением могут получать результаты, не укладывающиеся в основную разрядность процессора).

3) Счетчик команд

Счетчиккоманд (обозначаетсякакPC– ProgramCounterилиIP – InstructionPointer) является обязательным системным регистром. Значение этого регистра является адресом команды, которую выполняет процессор. Имя IP было выбрано для 8086 потому, что более совершенный контроллер памяти осуществлял упреждающее чтение команд из памяти. Поэтому тот адрес, который физически присутствовал на шине, не являлся адресом команды, которая в действительности исполнялась. Для отражения этого факта было выбрано имя «указатель на инструкцию» - т.е. значением регистраIP является адрес той команды, которая в данный момент исполняется.

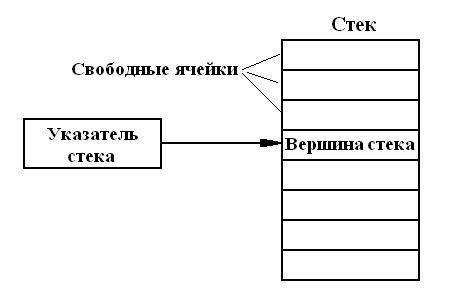

4) Указатель стека

Стек является повсеместно используемой структурой данных, обеспечивающей управление вызовами подпрограмм. Стек иначе называется памятью типа LIFO (LastIn – FirstOut, «последним зашел – первым вышел»). Визуально стек может быть представлен в виде стопки карточек, в которой новая карточка всегда кладется на самый верх, и снимается также сверху.

При вызове подпрограмм процессору необходимо нарушить последовательный порядок выполнения команд и перейти к новому адресу. По завершению работы подпрограммы исполнение следует продолжить с того места, откуда произошел вызов. Однако значение счетчика команд было потеряно, а это значит, что перед вызовом подпрограммы необходимо где-то сохранить тот адрес, из которого она вызывалась. Однако возможна ситуация, когда вызванная подпрограмма сама вызовет другую подпрограмму, поэтому ей также потребуется запоминать место, с которого произошел вызов. Глубина таких вложенных вызовов в целом заранее неизвестна (хотя, разумеется, из практических соображений она не может быть бесконечно большой). Для хранения адресов, из которых происходил вызов подпрограмм, и требуется стек. Помещение адреса на стек при вызове и снятие его со стека при завершении работы подпрограммы выполняется процессором автоматически (т.е. не должно быть специально организовано программистом). Адреса хранятся в обычной памяти, а начальный адрес помещается в указатель стека. Обычно указатель стека уменьшается при помещении нового адреса (в таких случаях говорят «стек растет вниз»). Это сделано для того, чтобы при заранее неизвестном объеме памяти, которая потребуется для стека, можно было разместить начальную ячейку стека в самой последней из доступных ячеек памяти (т.е. присвоить стеку максимально возможный адрес). Если обычные объекты программы начнут размещаться с минимальных адресов, стек не будет им мешать.

5) Индексный регистр

При необходимости организации блочных пересылок процессор может использовать специальные команды, которые будут автоматически использовать адреса, хранящиеся в этих регистрах. В процессоре 8086 имеются индексные регистры SI и DI, для которых доступны команды, перемещающие данные из ячейки с адресом SI в ячейку с адресом DI и одновременно увеличивающие или уменьшающие значения этих регистров. Таким образом, пересылка больших областей памяти может быть ускорена.

6) Счетчик цикла

Регистр CX имеет в процессоре 8086 дополнительную функцию – хранение счетчика цикла для одной итерации. В системе команд 8086 имеется специальная команда JCXZ (уменьшение регистра cx и переход, если он равен нулю). Она позволяет ускорять выполнение циклов со счетчиком, комбинируя декремент счетчика, проверку его на ноль и переход.

7) Регистр адреса

Регистр BX в процессоре 8086 имеет более широкие возможности участвовать в операциях формирования адреса.

8) Регистр флагов

Данный регистр является сводным представлением одноразрядных регистров, называемых флагами. Они используются для формирования особых признаков результата исполнения последней операции, или задают режимы работы процессора в каких-либо случаях.

Наиболее широко используемыми флагами являются:

– флаг переноса (CarryFlag) – равен 1, если в результате выполнения последней математической операции произошло переполнение или исчерпание разрядной сетки; показательным примером является прибавление единицы к максимальному числу; после выполнения логических операций этот флаг равен 0, поскольку результат вписывается в разрядность регистра;

– флаг нуля (ZeroFlag) – равен 1, если в результате выполнения операции был получен нулевой результат; некоторые арифметические команды могут не влиять на этот флаг (например, инкремент и декремент в 8086);

– флаг четности (ParityFlag) – равен 1, если результат имеет четное число установленных в 1 бит;

– флаг знака (SignFlag) – равен 0, если результат операции положительный, и 1 в противоположном случае;

– флаг переполнения (OverflowFlag) – схож с флагом переноса, однако переполнением считается не выход за пределы разрядной сетки, а пересечение границы положительных и отрицательных чисел; так, если для байта считается, что он представляет числа в диапазоне -128..+127, то операция 127 + 1 = 128 не вызовет переполнения разрядной сетки (флаг переноса равен нулю), но будет являться пересечением границы между положительными и отрицательными числами;

– флаг разрешения прерываний (InterruptFlag) – используется для управления исполнением прерываний; как правило, если этот флаг равен 1, процессор может реагировать на прерывания; такой глобальный флаг прерываний часто комбинируется с другими флагами или регистрами, чтобы разрешить реакцию на определенные типы прерываний.

Можно выделить три основных подхода к формированию регистров процессора.

1) Симметричная регистровая архитектура.

Используется также термин «регистровая архитектура».

2) Асимметричная регистровая архитектура

Для одной из разновидностей используется также термин «аккумуляторная архитектура».

3) Стековая архитектура.

Архитектура с симметричным набором регистров предполагает наличие в процессоре полностью равноправных регистров, каждый из которых может выступать в качестве операнда любой команды.

Рис. 5.7 Архитектура с симметричным набором регистров.

Как правило, в таком случае используется слабое кодирование, т.е. отдельные биты кода команды непосредственно кодируют номера регистров, участвующих в операции. Пример расшифровки кода команды при слабом кодировании показан на рис. 5.8.

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

c |

c |

c |

c |

z |

z |

z |

z |

y |

y |

Y |

y |

x |

x |

x |

X |

cccc – битовая комбинация, задающая тип команды (например, 0001 – сложение, 0010 – вычитание и т.д.);

xxxx – двоичное число, задающее номер первого операнда;

yyyy – двоичное число, задающее номер второго операнда;

zzzz – двоичное число, задающее номер регистра – получателя результата.

Рис. 5.8 Расшифровка кода команды для архитектуры с симметричным набором регистров.

На рис. 5.8 видно, что в наиболее общем случае, когда в команде участвуют три регистра, код команды должен содержать информацию обо всех этих регистрах. Предполагая, что процессор содержит 16 равноправных регистров, для задания номера каждого из них потребуется 4 разряда в поле команды. Для команды вида Rz = Rx + Ry, требуется 12 разрядов только для указания номеров всех регистров, участвующих в операции. Соответственно, большее количество регистров потребует большей ширины обязательных полей, кодирующих их номера. Из тех же соображений становится ясно, что для максимально эффективного использования кода команды следует выбирать количество регистров, равное целой степени двойки (4, 8, 16, 32 и т.д.).

Использование так называемых трехадресных команд (когда регистр-получатель может не совпадать ни с одним из операндов) представляет собой решение, при котором определяющим фактором при выборе архитектуры является максимальная функциональность системы команд, в том числе в ущерб размеру, занимаемому кодом. Например, в процессорах PowerPC, использующих 32 регистра общего назначения в сочетании с трехадресными командами, только для определения номеров регистров, участвующих в операции, требуется 15 бит в коде команды.

Процессоры x86 также имеют 4 симметричных регистра (EAX, EBX, ECX и EDX). Однако вместо трехадресных команд используется подход, в котором регистр-получатель совпадает с регистром, хранящим первый операнд команды. Иными словами, допустима команда addeax, ebx, складывающая eax и ebx и помещающая результат в eax, но недопустима команда вида addeax, ebx, ecx.

Симметричный набор регистров позволяет минимизировать число обращений к памяти в процессе выполнения сложных алгоритмов, требующих одновременного использования большого количества переменных. Поскольку в высокопроизводительных процессорах рабочая частота ядра обычно существенно выше рабочей частоты внешней памяти, данное решение позволяет существенно повысить общую производительность. Однако необходимо иметь в виду, что компилятор должен обеспечивать генерацию кода, эффективно использующего возможности процессора.

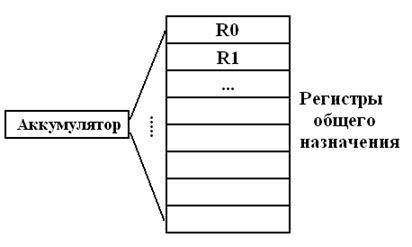

Асимметричная регистровая архитектура позволяет существенно уменьшить объем информации о номерах регистров за счет введения регистра-аккумулятора, получающего результат всех арифметико-логических команд. Если аккумулятор использовать и для хранения одного из операндов, то для описания команды достаточно указать номер единственного регистра, хранящего второй операнд. Асимметричная регистровая модель показана на рис. 5.9

Рис. 5.9 Асимметричная регистровая модель

Асимметрия показанной модели обычно распространяется и на команды пересылки, поэтому пересылка значения из одного регистра общего назначения в другой выполняется двумя командами (через аккумулятор). Такая модель предъявляет высокие требования к эффективности компилятора при работе со сложными алгоритмами, работающими с большим количеством переменных, однако хорошо подходит для реализации алгоритмов в стиле load/store, когда код состоит в основном из загрузки данных из памяти, выполнении несложных операций с ними, и записи полученного результата в память.

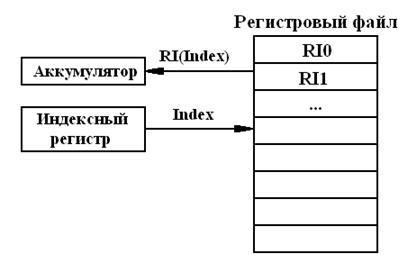

Разновидностью асимметричной архитектуры является модель с регистровым файлом (рис. 5.10). Регистровый файл подразумевает организацию регистров общего назначения в виде блока, адресуемого специальным индексным регистром. При этом число регистров может быть достаточно велико, поскольку n-разрядный индексный регистр способен адресовать 2n регистров. Все операции выполняются с операндами, хранящимися в аккумуляторе, и том регистре общего назначения, который выбран индексным регистром.

Рис. 5.10 Асимметричная архитектура с регистровым файлом

Главным достоинством регистрового файла является тот факт, что индексный регистр способен адресовать довольно большое количество регистров общего назначения. Однако необходимость постоянной перезагрузки индексного регистра является существенным недостатком. Очевидным решением, нивелирующим этот недостаток, является использование алгоритмов, не требующих частой смены индекса обрабатываемого регистра, или позволяющих использовать хорошо предсказуемый порядок смены индекса. Например, автоинкремент индексного регистра позволит путем повторения одной и той же команды выполнить некоторую операцию последовательно над всеми регистрами общего назначения, входящими в регистровый файл (или над некоторым диапазоном регистров).

Разновидностью регистрового файла является стековая архитектура, показанная на рис. 5.11.

Рис. 5.11 Стековая архитектура

Стековая архитектура является дальнейшим шагом в сторону сокращения информации о регистрах, передаваемой в команде. Регистровый файл при этом организован в виде LIFO (LastIn, FirstOut – «последний вошел, первый вышел»), то есть данные, загруженные в стек последними, будут использованы в первую очередь. Все операции над данными всегда выполняются над числами, находящимися на вершине стека. Результат также всегда помещается на вершину (обычно аргументы при этом удаляются). Преимуществом стековой архитектуры является минимальный набор команд, которые необходимо реализовать для получения полнофункционального процессора, поскольку каждая команда может работать только с одним набором регистров – парой, в настоящее время находящейся на вершине стека. Управление указателем стека обычно происходит неявно, то есть его значение не подлежит непосредственной модификации.

Очевидным решением для стековой архитектуры является использование сильного кодирования (т.е. в коде команды нельзя однозначно выделить отдельные разряды, отвечающие за то или иное действие или номера регистров). Поскольку номера команд в этом случае могут быть легко изменены, стековая машина часто используется при разработке промежуточных языков, обеспечивающих простой перенос между различными платформами (например, байт-код Java, или лежащий в основе технологии .netMSIL). При существенных ограничениях в реализации сложных алгоритмов стековая архитектура дает возможность использовать наиболее простые алгоритмы кодогенерации. Стековая модель представления данных напрямую используется в языке программирования Форт (Forth). Для стекового процессора команды языка Форт могут непосредственно совпадать с базовыми операциями процессора.

Отдельным вариантом являются векторные и DSP-ориентированные архитектуры. Их основным отличием является ориентация на выполнение одинаковых операций над группой данных (прежде всего, умножение с накоплением). Характерными чертами таких процессоров является большая разрядность и возможность группировки/разгруппировки регистров. Например, пара 128-разрядных регистров может быть использована в качестве четырех пар 32-разрядных регистров, причем одна команда может кодировать операцию, выполняемую над каждой из этих 4 пар в одном и том же такте. В остальном к DSP-процессорам применимы рассуждения, приведенные выше.

Вопрос выбора той или иной регистровой модели напрямую связан с требованиями системы, для управления которой проектируется процессор. Поэтому одним из путей разработки является создание ключевых алгоритмов программного обеспечения и анализ их основных особенностей. При этом можно будет определить основные требования к регистрам процессора, их количество и требуемый набор команд для реализации заданных алгоритмов, а также интенсивность передачи данных между регистрами общего назначения, что позволит уже на ранних этапах проектирования аппаратной части принять решение о необходимости реализации симметричной архитектуры (наиболее ресурсоемкой).