В проекте на VHDL могут быть следующие типы файлов:

- синтезируемые модули (VHDLmodule);

- библиотеки (VHDLlibrary);

- пакеты (VHDLpackage);

- описания тестов (VHDLtestbench).

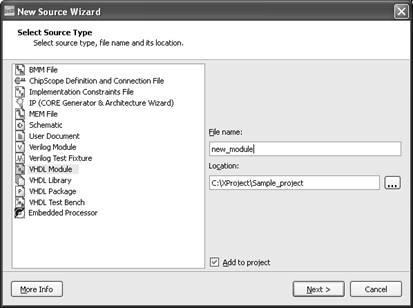

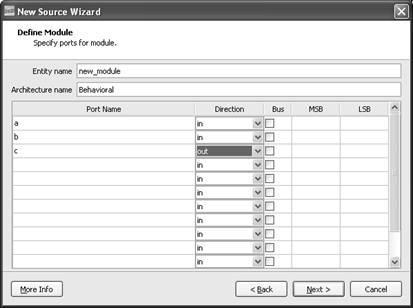

Рассмотрим процесс подключения модуля VHDL к проекту в САПР ISE. Это удобнее производить с помощью мастера создания новых компонентов (меню Project → NewSource, или из контекстного меню области Design). В диалоговом окне мастера создания нового компонента необходимо выбрать тип файла «VHDLModule» и ввести имя в поле FileName. На рис. показан пример создания нового модуля с именем new_module. После нажатия на кнопку «далее» будет необходимо ввести имена входных и выходных сигналов. Направление (вход, выход, двунаправленный сигнал) регулируется в выпадающем списке в колонке Direction.

Рис. 2.2 Окно создания нового компонента

Рис. 2.3 Настройка интерфейса создаваемого модуля VHDL

После ввода списка сигналов будет сгенерирован шаблон модуля VHDL, как показано в приведенном ниже листинге.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

--library UNISIM;

--use UNISIM.VComponents.all;

entitynew_module is

Port( a : in STD_LOGIC;

b : in STD_LOGIC;

c : out STD_LOGIC);

endnew_module;

architecture Behavioral of new_module is

begin

endBehavioral;

Анализируя листинг, можно выделить структуру модуля на VHDL. В первых строках модуля подключаются общеупотребительные библиотеки. Их состав и назначение будут рассмотрены позднее. Далее САПР ISE помещает в модуль две закомментированные строки, подключающие библиотеку UNISIM. Эта библиотека содержит компоненты, специфичные для ПЛИС Xilinx, и ее подключение сделает разрабатываемый модуль несовместимым с другими аппаратными платформами – ПЛИС других производителей и полупроводниковыми микросхемами. С другой стороны, использование аппаратных ядер и instantiated-компонентов невозможно без подключения данной библиотеки.

4Комментарии в VHDL задаются двумя минусами и действуют до конца строки.

Необходимо дать пояснение, что VHDL не содержит многострочных комментариев во избежание неоднозначностей в их интерпретации, как средствами синтеза, так и разработчиками при чтении исходных текстов модулей. Такое решение является элементом достижения повышенной надежности разработки на VHDL. При необходимости быстрого комментирования группы строк можно воспользоваться кнопками на инструментальной панели редактора, которые показаны на рис.

Рис. 2.4 Фрагмент инструментальной панели с кнопками для внесения и удаления символов комментария для выделенного фрагмента.

Далее в описании модуля находятся разделы entity и architecture. Пока можно вкратце упомянуть, что в разделе entity описываются «внешние» характеристики модуля, а в architecture – его реализация. В разделе architecture после ключевого слова begin размещается описание работы модуля, что будет подробнее обсуждено позже.