Аббревиатура UART обозначает UniversalAsynchronousReceiver-Transmitter – «универсальный асинхронный приемопередатчик»

Интерфейс RS-232 долгое время являлся стандартным последовательным интерфейсом для PC. Сопряжение устройства на базе ПЛИС с ЭВМ, выполненное без дополнительных внешних устройств (за исключением преобразователя уровней, таких как MAX232 или ADM232) предоставляет новые возможности как разработчику как этапе проектирования, так и пользователю созданного устройства. В настоящее время интерфейс UART («COM-порт») по-прежнему встречается в материнских платах десктопов. Ввиду простоты и широкой распространенности UART выпускаются различные преобразователи, например USB-UART, Ethernet-UART, WiFi-UART и т.д. Они дают возможность устройствам, не оборудованными UART, обмениваться данными с оборудованием, предусматривающим связь только в этом формате.

Разработка контроллера RS-232 позволяет продемонстрировать довольно эффективный прием проектирования на VHDL – реализацию конечных автоматов для выполнения относительно сложных операций.

Для асинхронной передачи по протоколу RS-232 достаточно всего двух сигнальных линий – TD (TransmitData) и RD (ReceiveData). Для электрического сопряжения сигналов потребуются стандартные устройства преобразования уровней RS-232 (лежащих в диапазоне –12¼+12В) в логические уровни ТТЛ/КМОП. После преобразования к выводам ПЛИС окажутся подключены два сигнала, которые можно обозначит как rx и tx.

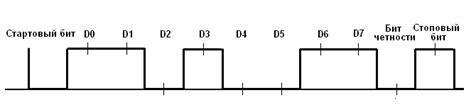

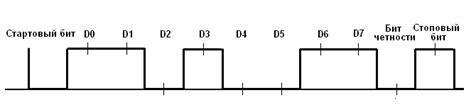

Протокол передачи по интерфейсу RS-232 представлен на рис.4.13. Передача начинается установкой низкого логического уровня на входе приемника. Низкий уровень сохраняется на время длительности одного бита, который называется стартовым. Далее передаются биты данных (число которых зависит от настроек протокола). В последовательных портах PC передача начинается с младшего бита. После передачи последнего бита данных вводится бит четности, формируемый по позитивной или негативной четности в зависимости от настроек протокола. Теми же настройками передача бита четности может быть отключена. В завершение передается стоповый бит, после которого линия остается в состоянии логической единицы вплоть до следующей посылки данных.

Рис. 4.13 Передача данных по протоколу RS-232

Асинхронный протокол передачи накладывает достаточно жесткие требования на стабильность интервалов времени, в течение которых передаются отдельные биты. Для повышения надежности передачи желателен прием отдельных битов возможно ближе к середине этих интервалов. С той же целью можно использовать довольно эффективный прием многократного считывания состояния линии с последующим подсчетом количества принятых нулей и единиц.

При реализации приемника в ПЛИС необходимо в первую очередь решить проблему задания временных интервалов. Действительно, если длительность отдельных битов и может быть определена исходя из известных настроек протокола передачи, то ПЛИС, вообще говоря, не имеет собственного устройства отсчета времени. Следовательно, для синхронизации необходимо использовать внешний тактовый сигнал, причем его частота должна быть достаточно большой для обеспечения хорошего разрешения по времени.

Наличие внешнего тактового сигнала и асинхронных сигналов, управляющих состоянием приемника, позволяют использовать технологию проектирования конечных автоматов. Под конечным автоматом понимается некое устройство, которое может находиться в фиксированном числе состояний, переходы между которыми совершаются при выполнении определенных условий. В ПЛИС внешний тактовый сигнал может быть эффективно использован для тактирования работы конечного автомата.

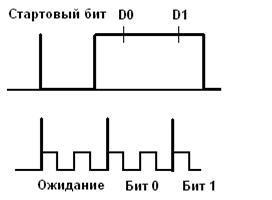

Рассмотрим временную диаграмму приема данных по последовательному интерфейсу. Передача данных начинается со стартового бита, причем время ожидания в общем случае не определено. Разумным решением будет ввод в состав конечного автомата (далее КА) состояния «ожидание начала». Из этого состояния его может вывести появление логического нуля на входе данных rx, что мы и отметим. После выхода из этого состояния необходимо подождать начала передачи младшего бита данных. В терминах КА это означает последовательный переход между вспомогательными состояниями. Эти переходы будут происходить с частотой следования внешних тактовых импульсов, и их количество (до середины младшего бита данных) определится длительностью стартового бита и половины длительности младшего бита данных.

Рис. 4.14 Диаграммы состояний конечного автомата приемника RS-232

Из рисунка видно, что длительности одного бита (стартового, стопового или данных) соответствует N тактов внешнего генератора. Следовательно, через N+N/2 тактов после начала стартового бита можно считывать младший бит данных, еще через N тактов – следующий бит и т.д. Всего до приема 8-го бита данных пройдет N + 7*N + N/2 тактов внешнего генератора. Поставим в соответствие каждому такту некоторое состояние конечного автомата и запишем последовательность переходов между состояниями.

|

Ожидание начала => Ожидание начала ИЛИ Стартовый бит Стартовый бит => перейти к считыванию бита данных 0 Бит данных 0 => перейти к считыванию бита данных 1 ... Бит данных 7 => формированию сигнала «принято» Принято => отключить сигнал «принято» и перейти к ожиданию начала

Остальные случаи => переход к следующему состоянию

|

При высокой частоте тактирования КА состояний оказывается довольно много. Однако ввиду простоты переходов между ними можно ввести переменную st (от state – состояние), которая будет хранить номер состояния КА. Пересчитав количество тактов (состояний) на один бит, можно получить номера состояний, в которых необходимо запоминать 0-й, 1-й, 2-й и т.д. биты данных.