Блоки комбинаторной логики добавляются с помощью оператора непрерывного присваивания.

q <= a and b;

q <= (a or b) xor (c and d);

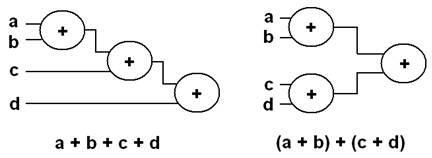

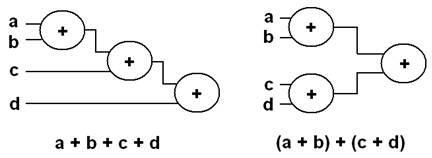

При необходимости приоритет операций регулируется скобками. Использование скобок также может быть полезно для управления процессом синтеза, поскольку в ряде случаев программы синтеза могут давать неоптимальные результаты. Например, результаты синтеза для выражения q = a + b + c + d и q = (a + b) + (c + d) могут оказаться различны – в первом случае будет синтезирована «лестничная» структура, где сигналы a и b пройдут последовательно через три сумматора, а во втором результаты окажутся чуть лучше, поскольку расстановка скобок заставит синтезатор создать два отдельных сумматора для выражений a + b и c + d, а затем сложить получившиеся выражения (рис.). Приведенные рассуждения справедливы только для достаточно сложных выражений, поскольку сложение (и любые другие операции) над 4 входными линиями в любом случае могут быть реализованы в одной LUT. Для прояснения вопроса рекомендуется использовать инструмент TechnologyViewer в ISE или SchematicViewer в Vivado, чтобы убедиться, что требуемая схема реализована рационально.

Рис. 4.1 Возможные результаты синтеза для эквивалентных арифметических выражений, различающихся расстановкой скобок

На уровне базовых примитивов комбинаторная логика может быть реализована путем прямого программирования LUT. Для этого необходимо подключить библиотеку UNISIM.VComponents (закомментированный шаблон для ее подключения уже присутствует в модулях, генерируемых САПР). В качестве примера приведен вентиль 2И, созданный путем прямого программирования LUT.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library UNISIM; -- необходимодобавитьобъявление

useUNISIM.VComponents.all; -- аппаратныхпримитивов

entitylut_struct is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : out STD_LOGIC);

endlut_struct;

architecture Behavioral of lut_struct is

begin

LUT2_inst : LUT2

generic map (

INIT => X"8") -– содержимое LUT

port map (

O =>c, --выходLUT

I0 =>a, -- первый вход LUT

I1 =>b -- второй вход LUT

);

endBehavioral;

В примере LUT подключена на структурном уровне – путем прямого указания компонента LUT2 (LUT с двумя входами) и цепей, которые подключаются к его выводам. Содержимое памяти LUT задано с помощью параметра INIT для модуля. В примере значение 8 соответствует таблице истинности для функции 2И. Заполнение таблицы, на первый взгляд, выглядит сложным, однако подчиняется довольно простым правилам. Рассмотрим таблицу истинности для функции 2И.

Таблица 4.1 Таблица истинности для функции 2И

|

a (0-й разряд входа) |

b (1-й разряд входа) |

C |

Номер позиции в LUT |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

2 |

1 |

1 |

1 |

3 |

Из табл. 5.1 видно, что значения, заносимые в память LUT для соответствия заданной функции, равны 1000 (заполнение начинается с младших разрядов). Таким образом, это число соответствует X”8”.

Проектирование комбинаторной логики на структурном уровне обеспечивает полный контроль над реализацией отдельных фрагментов, однако является наименее производительным способом разработки. Рекомендуется использовать такой подход только для наиболее критичных цепей проекта, для которых автоматический синтез дает очевидно неэффективную реализацию.

Шаблоны компонентов LUT находятся в справочной системе САПР. На VHDL необходимо подключать библиотеку аппаратных примитивов. Формально, каждое семейство FPGA имеет собственные аппаратные примитивы, однако FPGA серии 7 имеют одинаковые логические ячейки и перенос проектов на структурном уровне между ними выполняется без проблем.