Память является важным и часто используемым элементом современных цифровых устройств. Она представляет собой массив однотипных ячеек, хранящих число фиксированной разрядности. По характеру выполняемых с ней операций память подразделяется на:

– постоянные запоминающие устройства (ПЗУ, также ROM – Read-OnlyMemory), которые хранят фиксированные данные без возможности их изменения;

– оперативные запоминающие устройства (ОЗУ, также RAM – RandomAccessMemory), допускающие изменение записанных данных.

С точки зрения технической реализации память также имеет смысл подразделять на энергозависимую (сохраняющую данные только при поданном питании) и энергонезависимую. Для ранних вариантов исполнения энергонезависимая память являлась практически синонимом ПЗУ, поскольку техническая реализация таких микросхем подразумевала хранение данных в ячейках с пережигаемыми перемычками, ультрафиолетовым стиранием и т.п. Все эти принципы исполнения обеспечивали сохранность данных при отключении питания, но и не позволяли изменять содержимое памяти без специального оборудования – например, память с ультрафиолетовым стиранием требовала, как следует из ее названия, источника УФ излучения для стирания данных и специального программатора. В настоящее время существуют устройства энергонезависимой памяти, которые допускают изменение содержимого без специального программатора. Например, flash-память, память с электрическим стиранием (EEPROM), память FRAM, другие перспективные типы памяти. Часть из них требует отдельного цикла стирания, а часть позволяет произвольно перезаписывать данные, как для микросхем ОЗУ.

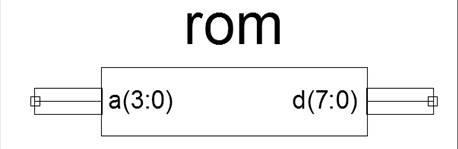

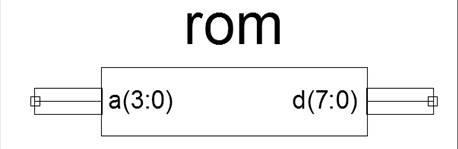

По способу организации интерфейса модули памяти подразделяются на модули с асинхронным или синхронным интерфейсом, а также с параллельным или последовательным доступом. Наиболее простой вариант – память с параллельным асинхронным доступом. Графическое изображение такого модуля показано на рис. 5.3

Рис. 4.3 Графическое изображение модуля памяти с асинхронным интерфейсом

Постоянное запоминающее устройство с асинхронным интерфейсом может быть описано с помощью оператора case.

При описании асинхронного ПЗУ с помощью оператора case используются строки вида <addr> :<data> - для каждого варианта адреса записывается то значение, которое хранится по этому адресу. Можно заметить, что при таком подходе сложно описать массивы памяти большого объема без применения средств автоматизации.

В ПЛИС модули ПЗУ небольшого объема обычно реализуются на базе логических генераторов программируемых ячеек. Ячейка с 6 входами (Virtex-5/6/7, Kintex-7, Spartan-6, Artix-7) может хранить 64 бита, а с 4 – 16 бит. Необходимо иметь в виду, что из-за реализации в виде мелких блоков память на базе программируемых ячеек не может обеспечить высокие характеристики производительности.

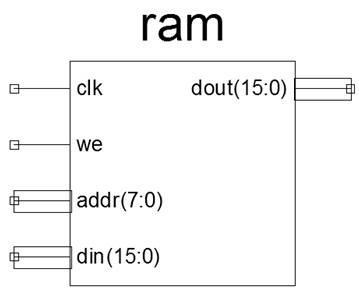

Синхронный интерфейс памяти обеспечивает более высокую производительность, поэтому память такого вида используется чаще. Блочная память, размещаемая в FPGA, является памятью с синхронным интерфейсом. Отличием такого типа интерфейса является выполнение всех действий по фронту тактового сигнала.

Для памяти с возможностью чтения и записи (ОЗУ) используются следующие дополнительные сигналы:

din – данные для записи;

we – разрешение записи (WriteEnable).

Память такого типа работает следующим образом: если по фронту тактового сигнала активен сигнал we, то производится запись данных din в ячейку памяти с адресом addr. Иначе производится чтение из памяти, и на выходе dout появляется содержимое ячейки памяти с адресом addr. Пример описания памяти с произвольным доступом с синхронным интерфейсом:

TypeTMemisarray (0 to 1023) ofstd_logic_vector(7 downto 0);

signalMem : TMem;

signalclk, we : std_logic

signal din, dout : std_logic_vector(15 downto 0);

signaladdr : integer range 0 to 255;

-- вразделеarchitecture

process(clk)

begin

ifrising_edge(clk) then

if we = ‘1’ then

Mem(addr) <= din;

end if;

dout<= Mem(addr);

endif;

endprocess;

Графическое изображение модуля показано на рис. 5.4

Рис. 4.4 Графическое изображение модуля ОЗУ с синхронным интерфейсом

Из описания порядка работы модуля ОЗУ виден его недостаток, проявляющийся в том, что при записи в память невозможно одновременно читать ее содержимое. Например, при использовании блока памяти для хранения таблицы значений, непрерывно выдаваемых на цифро-аналоговый преобразователь, устройство отображения информации или на иное устройство, требующее непрерывного потока данных, возникнет проблема, связанная с тем, что для обновления содержимого памяти придется прервать процесс чтения записанных в нее данных. От этого недостатка свободны многопортовые модули памяти, которые позволяют обращаться к одному и тому же массиву ячеек с помощью нескольких наборов линий addr, din, we, и имеют соответствующее количество выходных шин dout. Простейшим вариантом многопортовой памяти является двупортовая (dual-portmemory), которая имеет достаточно много разновидностей. По функциональным возможностям второго порта двупортовая память подразделяется на simpledual-port, или pseudodual-port («простая двупортовая», или «псевдо-двупортовая» память), и truedual-port («истинно двупортовая память»). Их отличием является то, что память truedual-port имеет два независимых и равноправных порта, по каждому из которых возможно проведение операций чтения и записи. У памяти simpledual-port один порт является универсальным (чтение и запись), а второй – только для чтения. Память такого типа вполне может быть использована в проектах, где требуется обеспечение непрерывного потока читаемых данных. В этом случае при необходимости перезаписи используется универсальный порт, а второй и используется для постоянного считывания. Графическое изображение simple dual-port памяти показано на рис. 5.5

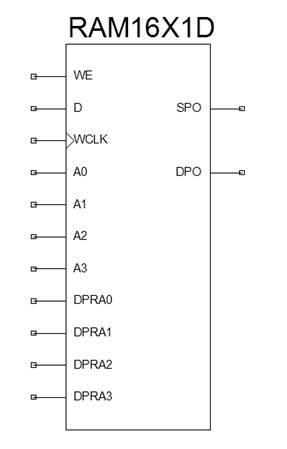

Рис. 4.5 Двупортовая память в конфигурации simpledual-port, построенная на базе логической ячейки FPGA

Логические генераторы программируемых ячеек FPGA представляют собой массивы статической памяти, хранящие таблицы истинности. Поэтому они могут быть использованы и в качестве модулей памяти, являясь при этом simpledual-port памятью. Такая память в терминологии FPGA называется также распределенной (distributed), поскольку распределена по программируемым ячейкам.

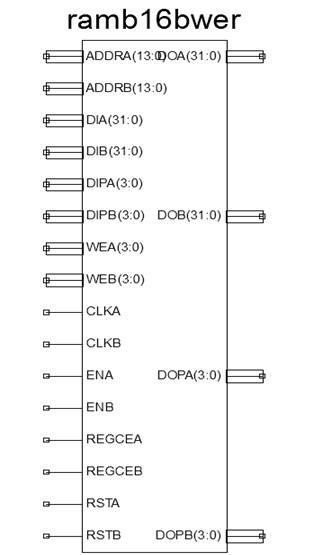

Блочная память, размещаемая в FPGA, является truedual-port («истинно двупортовая память»). Графическое изображение аппаратного примитива, представляющего собой наиболее полный вариант интерфейса, показано на рис. 4.6

Рис. 4.6 Графическое изображение блока памяти

Блок памяти имеет следующие порты:

– addra, addrb – адреса портов A и B соответственно;

– dia, dib – данные для записи для портов A и B (32 бита);

– dipa, dipb – дополнительные данные для записи (4 бита);

– wea, web – входы разрешения записи (побайтно);

– clka, clkb – тактовые сигналы для портов;

– ena, enb – входы разрешения работы блока памяти (при чтении состояние выходов не обновляется, если нет разрешающего сигнала);

– regcea, regceb – разрешение работы выходных регистров;

– rsta, rstb – сброс выходных регистров (не влияет на содержимое массивов памяти);

– doa, dob – выходы данных для портов A и B (32 бита);

– dopa, dopb – дополнительные выходы данных для портов A и B (4 бита).

Физически размещенные в FPGA блоки памяти являются 18-битными. Такая разрядность позволяет реализовывать схемы контроля четности, когда каждые 8 бит имеют дополнительный 9-й бит для хранения бита четности. Соответственно, каждые 16 бит имеют 2 дополнительных бита четности, а 32 – 4 бита. Для удобства работы с дополнительными битами в графическом представлении модуля они выделены в отдельные шины dipa, dipb, dopa, dopb.

Дополнительные биты не являются автоматически заполняемыми и представляют собой разряды, доступные для записи в них произвольных значений. Разработчик может выбирать требуемую ему разрядность, включая 9, 18 или 36 бит.

Блочная память является эффективным аппаратным ресурсом, который допускает работу на системной тактовой частоте. Это максимальная тактовая частота, на которой теоретически мог бы работать проект, если бы он не содержал цепей комбинаторной логики, проходящих более чем через один логический генератор, и слишком длинных трассировочных цепей. На практике работа на системной тактовой частоте оказывается доступной только для относительно компактных фрагментов проекта, и важно, что блочная память не ухудшает эти параметры. Следует также иметь в виду, что удельная стоимость блочной памяти ниже, чем памяти того же объема, реализованной на логических ячейках. Сложно указать точную границу объема, превышение которой делает блочную память однозначно более эффективным решением, однако можно ориентироваться на технические характеристики разных устройств (16x1 или 64x1 бит в логическом генераторе, 1024x18 бит в блоке памяти), а конкретный способ реализации памяти выбирать, исходя из доступных ресурсов проекта и требуемых технических характеристик.

Для принудительного использования заданного ресурса может потребоваться componentinstantiating, поскольку синтезаторы дляПЛИС при использовании автоматических настроек выбирают способ реализации памяти (блочная или распределенная), исходя из ее размера и режима работы (для truedual-port возможна реализация только в блочной памяти).

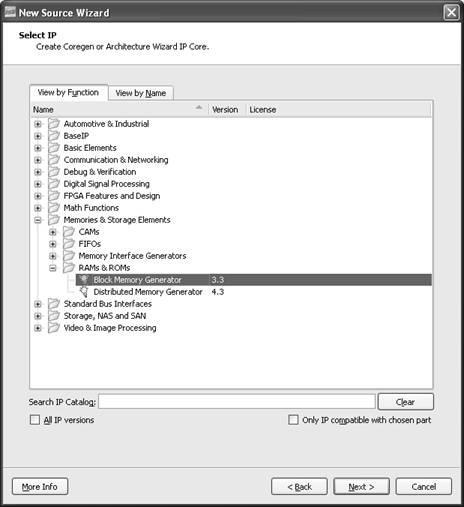

Приложение CoreGenerator входит в состав САПР ПЛИС ISE фирмы Xilinx и предлагает разработчику графический интерфейс быстрого конфигурирования стандартных цифровых блоков для реализации их в ПЛИС (IP-ядер). С помощью CoreGenerator имеется возможность создания шаблонов на языке Verilog, которые потом будут использованы как instance (см. componentinstantiation) в проектах пользователя. Генерация компонентов с помощью CoreGenerator обладает рядом преимуществ:

– IP-ядра, как правило, представляют собой верифицированные компоненты, имеющие качественное размещение на кристалле, и вследствие этого способные работать на высокой тактовой частоте;

– ряд специфичных ресурсов ПЛИС, например, модули формирования тактовой частоты, достаточно сложны для освоения, однако вносят в проект полезные функциональные возможности, поэтому рекомендуются к использованию; соответственно, CoreGenerator предоставляет возможности для их быстрого конфигурирования с последующим добавлением к проекту.

Рис. 4.7 Диалоговое окно выбора типа IP-ядра

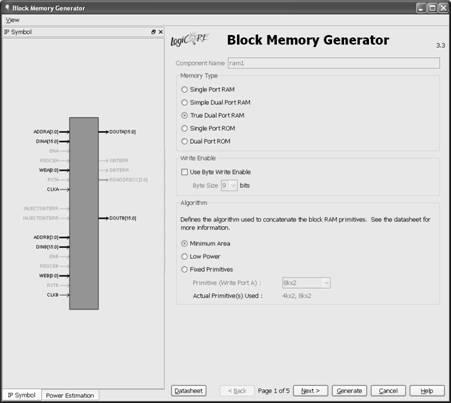

Рис. 4.8Диалоговое окно выбора типа блочной памяти

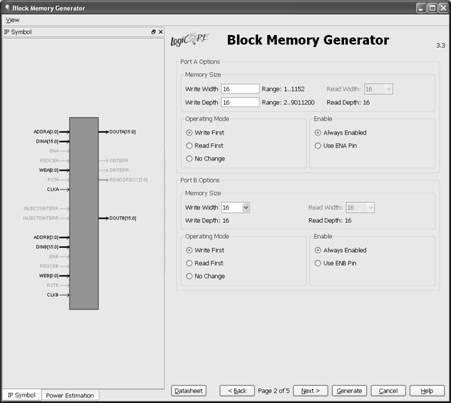

Рис. 4.9 Диалоговое окно настройки разрядности и глубины блочной памяти

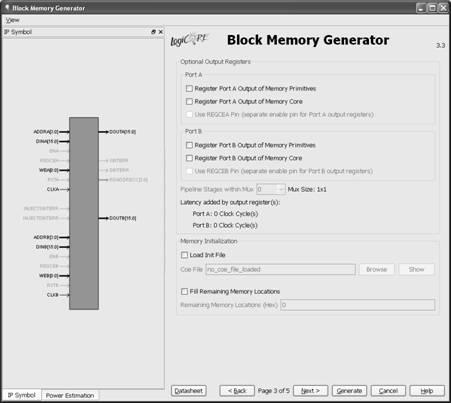

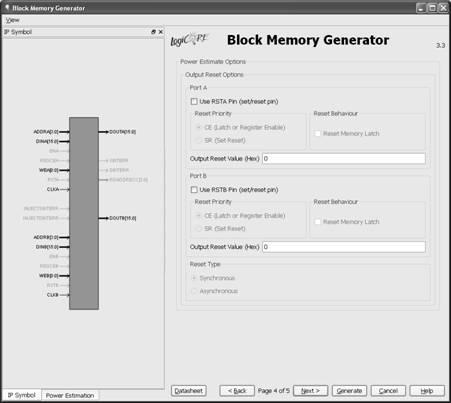

Рис. 4.10 Диалоговое окно настройки дополнительных параметров блочной памяти

Рис. 4.11 Диалоговое окно настройки дополнительных параметров блочной памяти

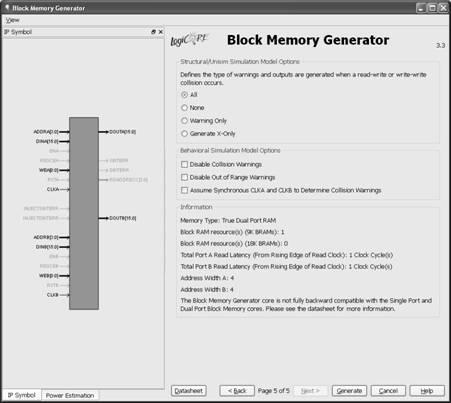

Рис. 4.12 Диалоговое окно подтверждения параметров IP-ядра блочной памяти